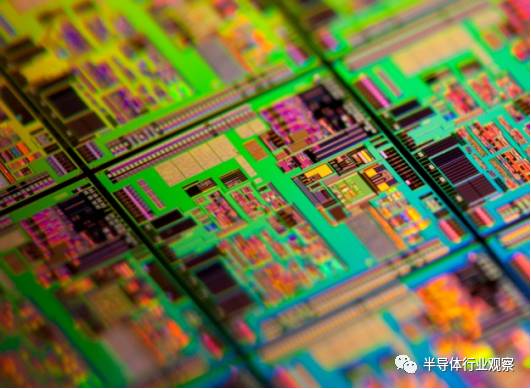

射頻(RF)集成電路是現代無線通信系統的核心,其性能直接影響著從智能手機到物聯網設備乃至衛星通信的方方面面。隨著半導體技術的不斷演進,傳統的GaAs、SiGe等III-V族化合物半導體工藝雖然在射頻領域一度占據主導地位,但深亞微米及納米級CMOS(互補金屬氧化物半導體)工藝憑借其卓越的集成度、成熟的產業鏈和極低的制造成本,已成為射頻集成電路設計的主流平臺。本文將探討基于CMOS工藝的RF IC設計中的核心考量、關鍵技術以及未來趨勢。

一、CMOS工藝進入射頻領域的優勢與挑戰

優勢:

1. 高集成度與SoC實現:CMOS工藝最突出的優勢在于能夠將復雜的數字基帶、模擬中頻電路和關鍵的射頻前端(如低噪聲放大器LNA、混頻器、壓控振蕩器VCO、功率放大器PA等)集成在單一芯片上,實現真正的片上系統(SoC),極大地減小了系統體積、功耗和成本。

2. 成本與產能:CMOS工藝依托于全球龐大的硅基集成電路生產線,量產成本極低,產能充足,這是任何專用工藝都無法比擬的。

3. 技術節點持續演進:隨著工藝節點從微米、深亞微米發展到納米級(如28nm、16nm、7nm甚至更先進節點),晶體管的截止頻率(fT)和最高振蕩頻率(fMAX)顯著提升,使得CMOS晶體管能夠勝任更高頻段(如毫米波)的射頻應用。

挑戰:

1. 器件性能固有局限:與GaAs等工藝相比,硅基CMOS晶體管的載流子遷移率較低,襯底損耗較高,導致其噪聲性能(如噪聲系數NF)、線性度和擊穿電壓等射頻關鍵指標存在先天不足。

2. 無源元件性能:片上電感、電容、變壓器等無源元件在低阻硅襯底上品質因數(Q值)較低,損耗大,限制了諧振電路(如LC振蕩器)的性能和集成濾波器的選擇性。

3. 襯底耦合與隔離:高集成度帶來的密集布局使得敏感的射頻模塊極易受到數字電路開關噪聲的干擾,襯底噪聲耦合問題嚴重,對電路與版圖的隔離設計提出了極高要求。

二、CMOS RF IC設計核心技術

為克服上述挑戰,設計師們發展了一系列專門的設計技術和架構:

- 電路拓撲與架構創新:

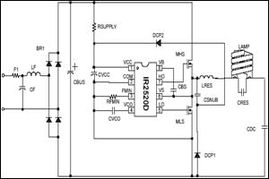

- 低噪聲放大器(LNA):廣泛采用共源共柵(Cascode)結構以提高增益和反向隔離,使用電感退化(Inductive Degeneration)技術進行噪聲匹配和線性化,并利用片上變壓器實現寬帶輸入匹配。

- 混頻器:吉爾伯特單元(Gilbert Cell)等有源雙平衡混頻器是主流,通過優化跨導級和開關級的設計來平衡轉換增益、噪聲和線性度。

- 壓控振蕩器(VCO):LC諧振腔VCO是首選,其核心在于設計高Q值的片上電感和變容二極管。采用互補交叉耦合結構(Cross-Coupled Pair)的負阻振蕩器能有效降低相位噪聲。

- 功率放大器(PA):這是CMOS RF設計中最具挑戰的環節。常采用開關模式(如Class D, E, F)或Doherty架構來提高效率,并使用堆疊晶體管(Stacked FET)技術來承受更高的輸出電壓擺幅。數字預失真(DPD)等線性化技術也常被集成以補償其非線性。

- 建模與協同設計:

- 精確的器件模型:依賴于工藝廠商提供的包含射頻寄生效應(如柵極電阻、襯底網絡)的精確晶體管模型(如BSIM-CMG, PSP)和無源元件模型。

- 電磁(EM)仿真:對于所有關鍵的無源元件(電感、變壓器、傳輸線)以及整體版圖的互連和耦合效應,必須進行全三維電磁場仿真,以確保仿真結果與流片結果的一致性。

- 版圖與隔離技術:

- 廣泛使用保護環(Guard Ring)、深N阱(Deep N-Well)、隔離槽(Trench Isolation)等技術來隔離射頻模塊與噪聲源。

- 采用差分電路設計以抑制共模噪聲和襯底耦合干擾。

- 對電源和地線進行精心設計,包括使用多重焊盤、片上解耦電容等,以降低電源阻抗和噪聲。

三、未來趨勢:向更高頻段與更高集成度邁進

- 毫米波與太赫茲應用:5G NR的毫米波頻段(24GHz以上)和未來6G對更高頻譜的探索,正推動CMOS RF IC設計向100GHz以上頻段發展。這需要利用工藝的極致速度,并研究新的波導、天線集成(AiP)技術。

- 數字輔助射頻技術:隨著工藝節點進步,數字電路的規模和能效優勢愈發明顯。數字輔助射頻(Digitally-Assisted RF)成為重要趨勢,例如使用數字校準來補償模擬電路的工藝偏差和溫度漂移,或采用全數字發射機/接收機架構。

- 異質集成與先進封裝:當單一CMOS芯片無法滿足所有性能需求時,通過硅通孔(TSV)、扇出型晶圓級封裝(Fan-Out WLP)、芯粒(Chiplet)等技術,將CMOS芯片與高性能的GaAs、氮化鎵(GaN)芯片或體聲波(BAW)濾波器進行異質集成,成為實現下一代高性能射頻前端模塊的關鍵路徑。

結論

基于CMOS工藝的射頻集成電路設計,是一場在工藝物理局限性與系統性能需求之間尋求最優解的精彩博弈。它已成功將射頻系統的成本降至前所未有的水平,并推動了全球無線通信的普及。面對未來更高速率、更高頻率和更復雜應用的需求,CMOS RF設計將繼續融合電路智慧、架構創新與系統思維,在納米尺度上譜寫無線連接的新篇章。