引言

在現(xiàn)代高速數(shù)據(jù)采集系統(tǒng)、醫(yī)療儀器、工業(yè)控制以及通信設(shè)備中,模數(shù)轉(zhuǎn)換器(ADC)扮演著將模擬世界與數(shù)字世界連接起來的關(guān)鍵角色。AD7862是一款由ADI公司生產(chǎn)的高性能、雙通道、12位、1MSPS采樣率的逐次逼近型(SAR)ADC,以其優(yōu)異的動(dòng)態(tài)性能和低功耗而著稱。為了充分發(fā)揮其性能,并實(shí)現(xiàn)靈活、可重構(gòu)的數(shù)據(jù)采集前端,現(xiàn)場(chǎng)可編程門陣列(FPGA)成為實(shí)現(xiàn)其接口與控制邏輯的理想平臺(tái)。本文將探討基于FPGA的AD7862接口電路的設(shè)計(jì)原理、關(guān)鍵模塊實(shí)現(xiàn)以及設(shè)計(jì)考量。

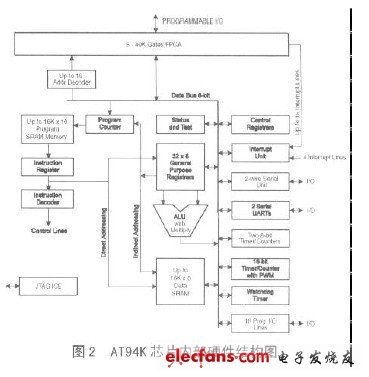

一、 系統(tǒng)架構(gòu)與設(shè)計(jì)目標(biāo)

基于FPGA的AD7862接口電路系統(tǒng)通常由以下幾個(gè)核心部分組成:

- 模擬前端調(diào)理電路:負(fù)責(zé)對(duì)輸入模擬信號(hào)進(jìn)行緩沖、縮放、濾波等處理,以滿足AD7862的輸入范圍和要求。

- AD7862芯片及其外圍電路:包括基準(zhǔn)電壓源、去耦電容、時(shí)鐘網(wǎng)絡(luò)等,確保ADC穩(wěn)定工作。

- FPGA核心控制邏輯:這是設(shè)計(jì)的核心,負(fù)責(zé)產(chǎn)生AD7862所需的所有控制時(shí)序(如CONVST、CS、RD等),讀取轉(zhuǎn)換后的數(shù)據(jù),并進(jìn)行可能的預(yù)處理(如數(shù)據(jù)對(duì)齊、格式轉(zhuǎn)換)。

- 數(shù)據(jù)輸出接口:將采集到的數(shù)據(jù)通過FPGA內(nèi)部總線(如Wishbone、AXI)或外部接口(如UART、SPI、以太網(wǎng))傳輸至處理器或上位機(jī)。

設(shè)計(jì)目標(biāo)主要包括:

- 時(shí)序精確性:嚴(yán)格滿足AD7862數(shù)據(jù)手冊(cè)中規(guī)定的建立/保持時(shí)間、脈沖寬度等時(shí)序參數(shù)。

- 高數(shù)據(jù)吞吐率:充分利用AD7862的1MSPS采樣能力,設(shè)計(jì)高效的數(shù)據(jù)流控制。

- 靈活性與可配置性:利用FPGA的可編程性,實(shí)現(xiàn)采樣率、通道選擇(雙通道順序或同時(shí)采樣模式)等參數(shù)的靈活配置。

- 穩(wěn)定性和抗干擾能力:良好的PCB布局布線及電源完整性設(shè)計(jì),確保數(shù)字噪聲對(duì)模擬信號(hào)的干擾最小化。

二、 關(guān)鍵接口信號(hào)與FPGA邏輯設(shè)計(jì)

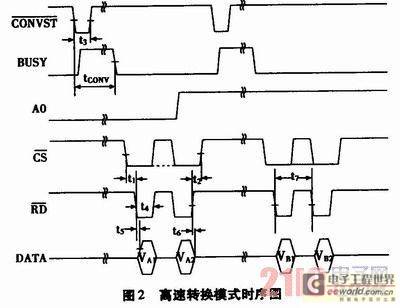

AD7862的主要控制信號(hào)包括:

- CONVST(轉(zhuǎn)換啟動(dòng)):下降沿啟動(dòng)A/D轉(zhuǎn)換過程。其頻率直接決定了采樣率。

- CS(片選)與 RD(讀使能):用于從ADC輸出寄存器中讀取數(shù)據(jù)。通常需要配合使用。

- BUSY:輸出信號(hào),高電平表示轉(zhuǎn)換正在進(jìn)行,下降沿表示轉(zhuǎn)換完成,數(shù)據(jù)已準(zhǔn)備好。

- DB0-DB11:12位并行數(shù)據(jù)輸出總線。

在FPGA內(nèi)部,可以使用有限狀態(tài)機(jī)(FSM)來精確控制整個(gè)“啟動(dòng)轉(zhuǎn)換-等待完成-讀取數(shù)據(jù)”的循環(huán)。一個(gè)典型的狀態(tài)機(jī)可以設(shè)計(jì)為四個(gè)狀態(tài):

- IDLE:空閑狀態(tài)。等待啟動(dòng)信號(hào)或內(nèi)部定時(shí)器觸發(fā)。

- START_CONV:拉低CONVST信號(hào),啟動(dòng)一次轉(zhuǎn)換,然后進(jìn)入等待狀態(tài)。

- WAIT_BUSY:監(jiān)控BUSY信號(hào),等待其從高變低(轉(zhuǎn)換完成)。

- READ_DATA:在BUSY變低后,操作CS和RD信號(hào),將數(shù)據(jù)總線上的值鎖存到FPGA內(nèi)部寄存器中。完成后返回IDLE狀態(tài),準(zhǔn)備下一次轉(zhuǎn)換。

對(duì)于雙通道操作,需要根據(jù)AD7862的模式選擇引腳(MODE)進(jìn)行配置,并在狀態(tài)機(jī)中增加通道選擇與控制邏輯。

三、 集成電路設(shè)計(jì)考量

雖然FPGA實(shí)現(xiàn)了數(shù)字接口邏輯,但整個(gè)系統(tǒng)作為一塊集成電路板,其設(shè)計(jì)質(zhì)量至關(guān)重要:

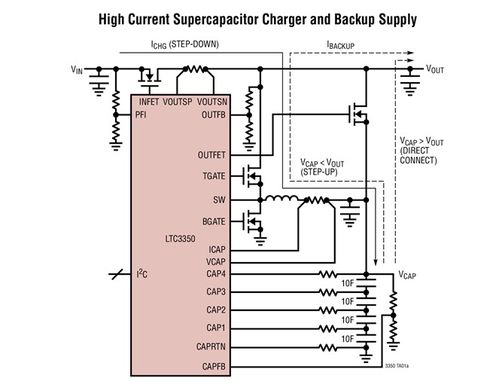

- 電源與地設(shè)計(jì):AD7862要求高品質(zhì)的模擬電源(+5V AVDD)和數(shù)字電源(+5V DVDD)。必須使用磁珠或電感進(jìn)行隔離,并布設(shè)充足的去耦電容(通常為0.1μF陶瓷電容靠近電源引腳,并輔以10μF鉭電容)。模擬地和數(shù)字地應(yīng)在芯片下方單點(diǎn)連接。

- 基準(zhǔn)電壓源:AD7862內(nèi)置2.5V基準(zhǔn),也可使用外部更高精度的基準(zhǔn)(如ADR421)。基準(zhǔn)引腳必須用低ESR電容充分去耦。

- 信號(hào)完整性:

- 模擬輸入路徑:應(yīng)盡量短,并采用屏蔽或用地線包圍,遠(yuǎn)離高速數(shù)字信號(hào)線。串聯(lián)小電阻有助于減少反射。

- 數(shù)字信號(hào)線(特別是CONVST和時(shí)鐘):應(yīng)視為傳輸線,必要時(shí)進(jìn)行端接匹配,以減少振鈴和過沖,確保時(shí)序邊緣清晰。

- 數(shù)據(jù)總線:走線應(yīng)等長,以減少數(shù)據(jù)偏移(skew),保證FPGA能同時(shí)捕獲所有位。

- 時(shí)鐘管理:AD7862的轉(zhuǎn)換時(shí)鐘可由內(nèi)部產(chǎn)生或外部提供。若使用外部時(shí)鐘,需確保其干凈、穩(wěn)定。FPGA產(chǎn)生的CONVST信號(hào)也應(yīng)有低抖動(dòng)的時(shí)鐘源驅(qū)動(dòng)。

四、 FPGA內(nèi)部的高級(jí)功能集成

利用FPGA的并行處理能力和豐富資源,可以在接口邏輯之上集成更多功能,提升系統(tǒng)集成度:

- 數(shù)據(jù)緩存:使用FPGA內(nèi)部的Block RAM或FIFO,構(gòu)建數(shù)據(jù)緩沖區(qū),以匹配ADC高速輸出與后續(xù)相對(duì)低速處理或傳輸之間的速率差異。

- 實(shí)時(shí)處理:可集成數(shù)字濾波器(如FIR、IIR)、平均值計(jì)算、峰值檢測(cè)等預(yù)處理算法,減輕后端處理器的負(fù)擔(dān)。

- 多芯片同步:對(duì)于需要多片AD7862同步采樣的應(yīng)用,F(xiàn)PGA可以產(chǎn)生全局同步的CONVST信號(hào),實(shí)現(xiàn)精確的通道間同步。

- 自測(cè)試與校準(zhǔn)邏輯:可以設(shè)計(jì)邏輯,周期性地向ADC輸入已知的測(cè)試信號(hào)(或利用內(nèi)部特性),監(jiān)測(cè)其輸出,實(shí)現(xiàn)系統(tǒng)的在線自檢和軟件校準(zhǔn)。

五、 驗(yàn)證與測(cè)試

設(shè)計(jì)完成后,必須進(jìn)行 rigorous 的驗(yàn)證:

- 功能仿真:使用ModelSim等工具,編寫測(cè)試平臺(tái)(Testbench),模擬AD7862的行為模型,驗(yàn)證FPGA狀態(tài)機(jī)邏輯和時(shí)序的正確性。

- 時(shí)序分析:在FPGA綜合布局布線后,進(jìn)行靜態(tài)時(shí)序分析(STA),確保所有路徑滿足建立和保持時(shí)間要求,特別是與ADC接口的關(guān)鍵路徑。

- 板級(jí)測(cè)試:

- 使用示波器測(cè)量關(guān)鍵控制信號(hào)(CONVST, BUSY, RD)的時(shí)序關(guān)系,確保符合數(shù)據(jù)手冊(cè)要求。

- 使用信號(hào)發(fā)生器輸入標(biāo)準(zhǔn)正弦波,采集數(shù)據(jù)并分析其信噪比(SNR)、有效位數(shù)(ENOB)等動(dòng)態(tài)性能指標(biāo),評(píng)估整個(gè)系統(tǒng)的實(shí)際性能。

結(jié)論

基于FPGA的AD7862接口電路設(shè)計(jì),是一個(gè)融合了模擬電路設(shè)計(jì)、數(shù)字邏輯設(shè)計(jì)和高速PCB設(shè)計(jì)技術(shù)的綜合性項(xiàng)目。通過精心設(shè)計(jì)FPGA內(nèi)部的狀態(tài)機(jī)控制邏輯,并嚴(yán)格遵守ADC的模擬和數(shù)字接口要求進(jìn)行板級(jí)集成電路設(shè)計(jì),可以構(gòu)建一個(gè)高性能、靈活可靠的數(shù)據(jù)采集系統(tǒng)。FPGA的可編程特性為進(jìn)一步的系統(tǒng)功能集成和優(yōu)化提供了無限可能,使得該方案在眾多高要求的工業(yè)與科研領(lǐng)域具有廣泛的應(yīng)用前景。